田島OMの製作した、DLL制御基板(左下) 右下はELECRAFT社のK1トランシーバー

実験中の様子

DLL-VFOの製作

JA1XFA 田島OMの製作記事。

2013/12/21

2013年11月末、私宛てに一通のメールが到着しました。

内容は、このホームページに掲載してあるDLL-VFOに、興味を持たれたとの、内容です。

それも何と、米国ELECRAFT社のK1トランシーバーに組み込みたいとの、内容でした。

K1のVFOは、LC-VFOの様で、普通に考えれば実用上問題ない安定度は、有ると思うのですが、

あえて、DLL-VFOを組み込みたいとの、事でした。

DLL-VFOのPICソフトを、解析して、直ぐに、K1用に変更され、私の元へソースファイルが届きました。

K1は、デジタル表示器が付いていて、液晶表示は不要の様です。又、VFOもK1の物を使用するので、

VFOも不要の様です。

変更された、ソフトは、綺麗に書かれていました。早速(結構掛かってしまいましたが・・)、私も実際に動くか、

実験用に作った基盤で、試験しましたが、一発で動きました。ん~、流石と、云う感じでした。

その間、田島OMの方は、K1の改造と、DLL-VFOの製作をしていた様です。

あっさり、改造も、終わり、いざ、実機運転です。しかし、ここは、流石に田島OMでも、一発では動かなかった様です。

その後何度か、質問が来ましたが、ソフトは私も実証済みなので、ソフトは大丈夫ですと、一点張りでした。

しかし、ソースネタは、私なので、本当の所は、すべてに於いて、心配でした。特にハードは、自信が有りません。

まして、全てコピーで有ればある程度予想は付くのですが、PICの部分のみ使用して、その他は、K1のシステムを、

使うので、 しかし基本は、LC-VFOを安定にするだけなので、理屈では、問題ないとも、思っていました。

その後、「動作しました。」 との、メールが届き安心しました。

内容は、下記で田島OM直筆です。

こんにちは。高石OM。

DLL基板が動作しました。

動作しなかった原因

1.カウンタ部の信号レベル不足(^^;

2.フォトカプラTrのコレクタエミッタ間飽和電圧の見落とし

これが判りませんでした。合計で約1.4V位の電圧が残ってしまうためVCOの同調電圧範囲をカバーできず、

発振周波数が初期起動値に達しなかったため、???と悩んだ次第です。

K-1のVFO電圧は6Vでバンドエッジでバリキャップに掛かる電圧はおよそ5Vでしたが、

DLLで出力できる電圧は4.3Vまでしか上がらなかったためです。

これは回路内で12V→8V→6Vと2段階に落としているので8V系からバリキャップ制御電圧を取るようにして

(結果的には簡単に)解決しました。

配線図その他は整理中です。

まだRIT関連をチェックしていませんので仮接続で試していますが、7MHzの移動局のJCCサービスなどをワッチしていても

VFO部分が剥き出し状態なのにトーンが変わらず聞こえるのはとてもFBです。

ロータリーエンコーダでの操作性もFBです。平滑用コンデンサは私の場合はもう少し小さくても良さそうに思いますが。

と、頂きました。

これ、私は、大変もうれしかったです。

その後実機でも交信され様です。

しかし、まだまだ問題点が多い様で、

内容は、下記で田島OM直筆です。

プログラムで変更した最も大きな部分は、"少々のQRHは補正しない(^^;"ようにしたことです。

理由は、こうしないと送信中でも頻繁に周波数制御が掛かってしまって送信波が疑似FMされた

ようになりトーンが濁ってしまうためです。

CWなので余計目立つのかもしれませんが。

K-1はもともと自励VFOですので、短時間安定度は許容範囲であるため、

最初は「送信中は制御しない」ようなプログラムにしていましたが、やはり制御できるのをしない、

というのも無意味ですので、ではどうするかと考えた次第です。

記憶周波数と直前計測周波数が一致したら(QRH無しなら)制御をしない、という処理は簡単なので入れてみたのですが、

自励発振回路では全く変動しないというのは実質不可能なため、この周波数比較する32ビットデータの最下桁2ビットに

マスクを掛け「ちょびっとのQRHは無視、3ビット以上QRHしたら制御をする」という動作に変更したら概ね

満足できる状況になりました。

実はオリジナルの常時制御状態だと送受信トーンが震えてしまって聞き難い状況でしたので、

その対策で上記変更を行い、ついでに送信状態でも同じ条件での制御処理にした次第です。

勿論、送受信途中で制御が入るとトーンが少し変化しますが、VFOがある程度安定すると

制御介入回数も減少するので、こんなものかな?と考えています。

実はまだRIT制御を接続したらチャピらないか?とか、大幅QSYの際には周波数ピッチを変更したい、

とか未解決どころか、未確認事項が沢山溜まっておりますが、年末年始は、

コキ使われる運命で時間が取れるかどうか判らないので、取り敢えずの報告を差し上げた次第です。

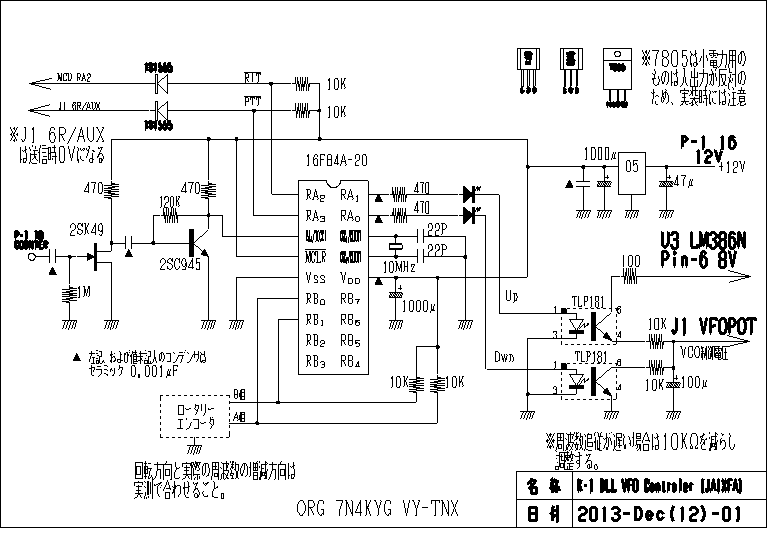

なお、配線図中の充放電用抵抗の値は最初は10KΩでしたが、

RIT制御の際クイックQSY対応ということで1KΩに変更してあります。と、細かく説明が入っていました。

いずれにせよ、問題点は、まだまだ有ると思いますが、CWでの報告は大変有り難いものでした。

以後、進展有りましたら、更新させて頂きます。

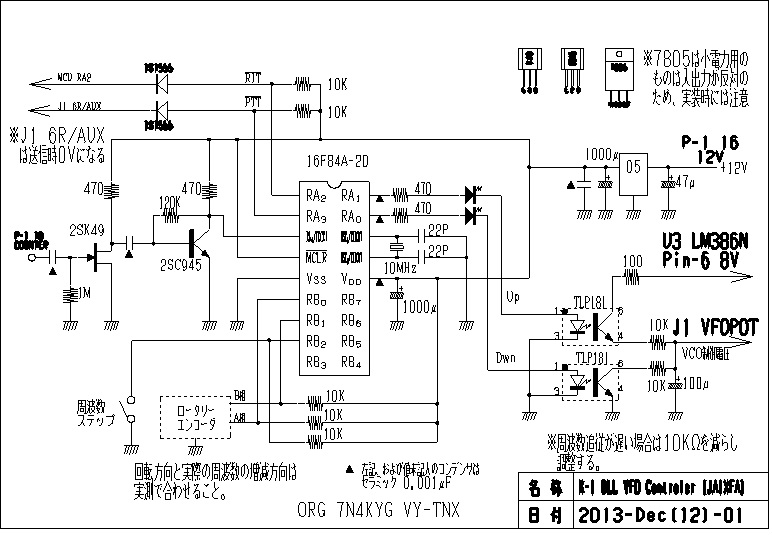

下記に田島OMの実験中の、写真、回路図を貼り付けました。

最終版(2014/01/27)現在-JA1XFA-K1用-DLL-VFO(改)のソフトは、ここをクリック

田島OMの製作した、DLL制御基板(左下) 右下はELECRAFT社のK1トランシーバー

実験中の様子

回路図 (最終回路図は、一番最後です。)

2014/01/27

田島さんから、完成のメッセージ頂きました。

K1対応の、DLLは、動く様に成った様ですが、それまでの過程のダイジェストを書きました。

ここでの内容は、RITの組み込みについてです。

赤文字は、田島OMの直筆です。

こんにちは。

やっとこさでK-1 DLLにRIT回路を実装しましたのでソースを送ります。

実装できるまではパズルでしたが、毎夜?風呂の中で考えていたらアイディアが浮かび動作にこぎつけました。

改めて言うまでもありませんが、当方の思っていたRIT動作とは、

1.送信時にはRITオフ時の周波数で送信する。

2.受信時には“任意の周波数”を受信できる。

3.RITをオフとすると受信周波数はオンにする前の周波数に戻る。

つまり送受信周波数は一致する。

4.RITオンの間はロータリーエンコーダを回しても送信周波数は固定される。

というものです。

上記1~4の仕様が最良かどうかは判りませんが、少なくとも当方がいままで使用していたリグの取り扱いと同等ですので、

これでしばらく使ってみたいと思います。

配線図のBMPファイルも同封します。以前の送ったものと、多分ほとんど同様ですが、同調ダイヤルのステップ可変のために

RB2にスイッチを一つ増やしました。

なお当SWを設けなくても動作には支障はありません。

ワッチで使って感じるのは、時々自動補正されて周波数がふにゃっ?といった感じで動きます。(^^;

DLLの性格上、特にCWの様なキャリアのみの受信の場合は、有り得ます数十hzは、ふらふらします。

ま、これはそれなりに時間が経てばVFOも安定するし、動く範囲も最小ステップ内ですので慣れるよりほか無さそうです。

DLLの特徴として、周波数カウントのゲートタイムが必要(当たり前)なため、周波数カウントをやっている間は送受の判定や

RITのオンオフを判定できません。

つまり、単純に考えてゲートタイムで必要な時間より短い間隔での送受切り替え(例えばフルブレークインへの対応)は難しそうです。

周波数安定化、という本来の目的は達せられたので、これ以上の機能を目指すかどうかは、しばらく使ってから考えたいと思います。

又、つい数日前、下記の内容のメッセージ頂きました。

下記は、ロータリーエンコーダーのチャタリングに付いてです。

機械式の場合の内容です。

こんにちは、高石さん。

チャタリング対策をやってみました。

PICの RB0/RB1 端子に手持ちの 0.47uF

の積層セラミックコンデンサを付けてみたところ、非常に効果がありました。

今まではエンコーダを回したときに、時として周波数が飛んだり、戻ったりと、妙な増減現象があったのですが、

ほぼ無くなりエンコーダを回すと、とてもスムーズに周波数が可変するように改善できました。

まじめ?に対策するならローパス構成にするか、シュミットトリガでも付けてやれば、もっと効果はありそうですが、

コンデンサ2個で概ね(いわゆる限界条件の試験は未実施なので)良好な結果になってしまいましたので、これで良し!にします。

と、云うことで、DLLについては、完成した様です。

性能は、DDSやPLLには、かなわないと思いますが、特別な部品を使わないので、手軽に出来る割には、

満足した性能が得られるのかな?、と云う感じと、思います。

PICの書込ツールも、現在は、安く入手出来ますので、興味が有ったら、いたずらして見て下さい。

ソフトも、初めて見ると難しそうですが、一寸した改造、(周波数を変更)は、簡単に出来ると思いますので、

5MHZ程度以下のVFOのRIGでしたら、応用は比較的簡単に出来ると思います。

最終回路図を下記に示します。

ソフトも最終版に変えました。